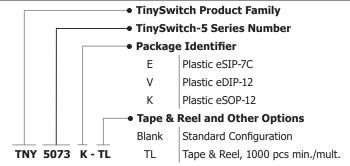

# **TinySwitch-5** Family

Integrated Off-Line Switcher with EcoSmart Technology for Highly Efficient Power Supplies

#### **Product Highlights**

#### **Highly Integrated, Compact Footprint**

- Robust 725 V silicon MOSFET provides excellent surge withstand

- Switching frequency up to 150 kHz minimizes transformer size

#### EcoSmart<sup>™</sup> – Energy Efficient

- Up to 92% efficient, flat across load range

- Less than 30 mW no-load power at 230 VAC including line sense

- Up to 210 mW output power for 300 mW input (230 VAC)

- · Lossless primary current sensing

### **Reduced Part Count, Design Flexibility**

- Frequency jitter reduces EMI filter size

- Integrated soft-start minimizes start-up stress

- Adjustable switching frequency

#### **Extensive Protection**

- Auto-restart limits power delivery to <3% during output short circuit faults

- Output short-circuit, overload and overvoltage protection

- · Line undervoltage (UV) detection prevents turn-off glitching

- · Simple, fast AC reset

- Line overvoltage (OV) shutdown

- · Accurate thermal shutdown with large hysteresis (OTP)

#### **Typical Applications**

- Auxiliary, standby and bias power supplies for appliances, and consumer products

- · Utility meter, smart grid and industrial power supplies

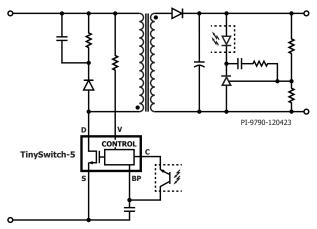

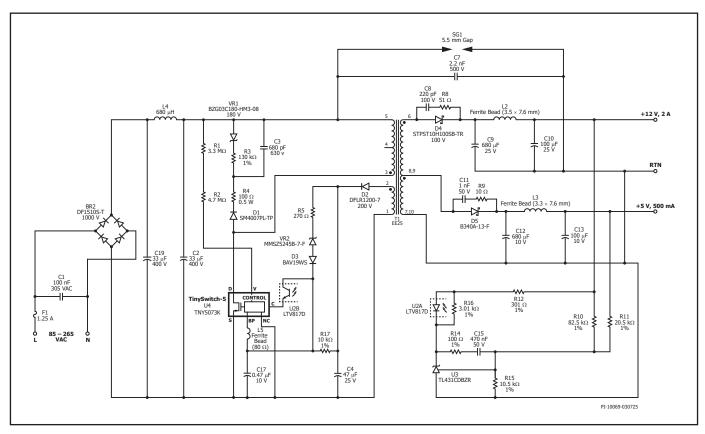

Figure 1. Typical Flyback Application.

| Product     | Output Power (W) |           |            |  |  |  |

|-------------|------------------|-----------|------------|--|--|--|

| Туре        | 400 VDC          | 230 VAC   | 85-265 VAC |  |  |  |

| eSOP-12 (K) | 25 - 75          | 22 - 70   | 15 - 45    |  |  |  |

| eDIP-12 (V) | 25 - 75          | 22 - 70   | 15 - 45    |  |  |  |

| eSIP-7 (E)  | 120 - 190        | 105 - 175 | 70 -120    |  |  |  |

Table 1. Power Range by Package Type.

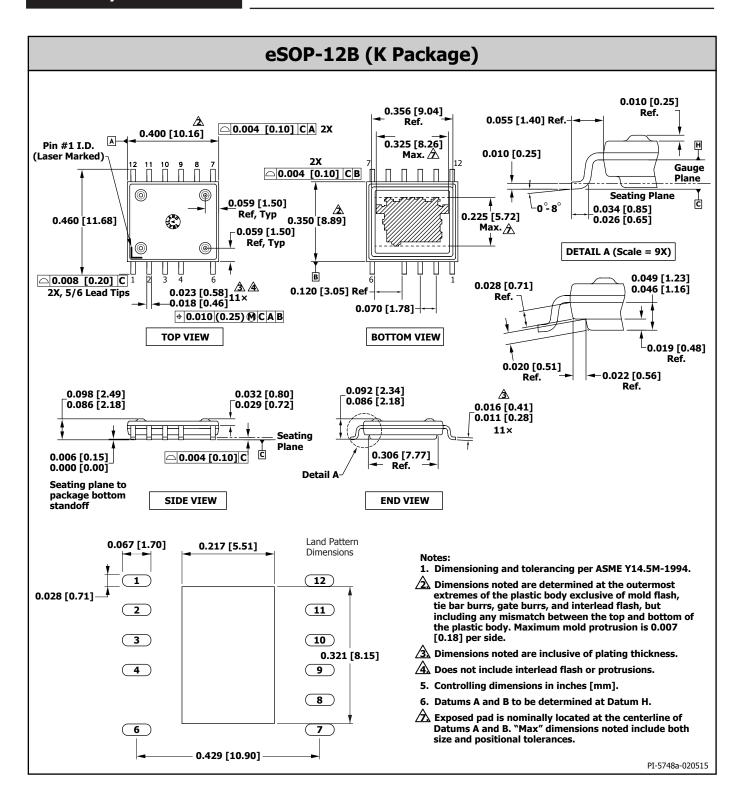

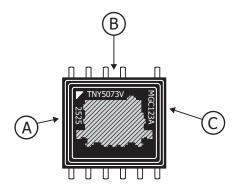

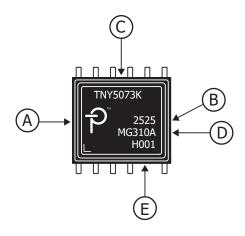

#### eSOP™-12 Package (K Suffix)

- Low profile surface mount package ultra-slim designs

- · Supports wave or reflow soldering

- PCB cooling via SOURCE pin and exposed pad for low EMI

### eDIP™-12 Package (V Suffix)

- Low profile horizontal orientation for ultra-slim designs

- · Suitable for Top heatsink and reflow

- Thermal impedance equivalent to a TO-220 package

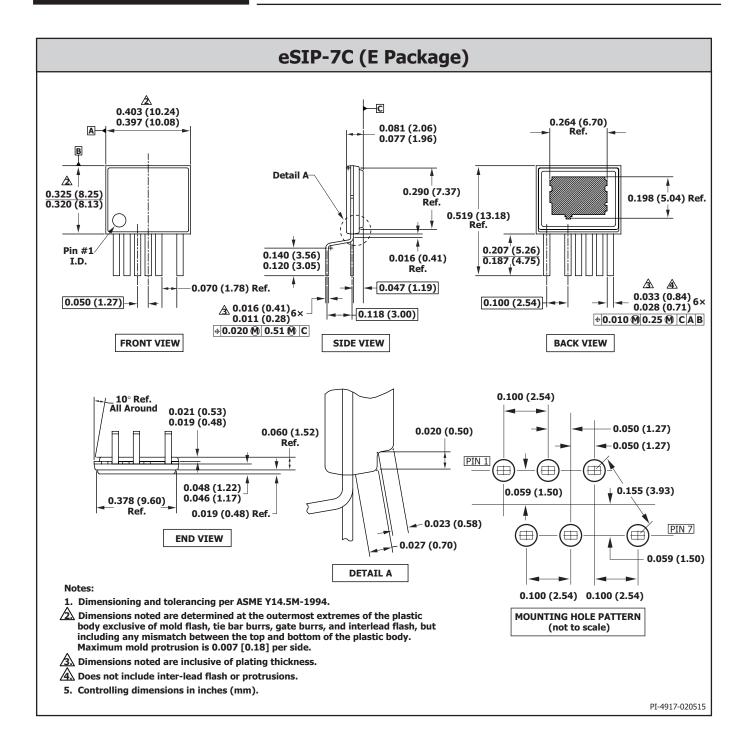

#### eSIP™-7 Package (E Suffix)

- Vertical orientation for minimum PCB footprint

- Simple heatsink mounting using clip

- Thermal impedance equivalent to TO-220 package

- Provides extended power range

### Output Power Table<sup>1</sup>

|                      |                                      | РСВ Сор                              | per Area¹                            |                      | Metal Heatsink <sup>1</sup>          |                                      |                                      |  |

|----------------------|--------------------------------------|--------------------------------------|--------------------------------------|----------------------|--------------------------------------|--------------------------------------|--------------------------------------|--|

| Product <sup>3</sup> | 400 VDC                              | 230 VAC ±15%                         | 85-265 VAC                           | Product <sup>3</sup> | 400 VDC                              | 230 VAC ±15%                         | 85-265 VAC                           |  |

|                      | Peak or<br>Open Frame <sup>2,3</sup> | Peak or<br>Open Frame <sup>2,3</sup> | Peak or<br>Open Frame <sup>2,3</sup> |                      | Peak or<br>Open Frame <sup>2,3</sup> | Peak or<br>Open Frame <sup>2,3</sup> | Peak or<br>Open Frame <sup>2,3</sup> |  |

| TNY5071K             | 25 W                                 | 22 W                                 | 15 W                                 | TNVE071V             | 25 W                                 | 22 W                                 | 15 W                                 |  |

| TNY5071V             | 25 W                                 | 22 W                                 | 15 W                                 | TNY5071V             | 25 W                                 | ZZ_VV                                | 15 W                                 |  |

| TNY5072K             | 35 W                                 | 32 W                                 | 20 W                                 | TNY5072V             | 35 W                                 | 32 W                                 | 20 W                                 |  |

| TNY5072V             | 35 W                                 | 32 W                                 | 20 W                                 |                      | 35 W                                 | 32 W                                 | 20 VV                                |  |

| TNY5073K             | 50 W                                 | 45 W                                 | 30 W                                 | TNVEOTOV             | E0.W                                 | 4E W                                 | 20 W                                 |  |

| TNY5073V             | 50 W                                 | 45 W                                 | 25 W                                 | TNY5073V             | 50 W                                 | 45 W                                 | 30 W                                 |  |

| TNY5074K             | 60 W                                 | 55 W                                 | 35 W                                 | TNY5074V             | 60 W                                 | 55 W                                 | 35 W                                 |  |

| <b>TNY5074V</b>      | 60 W                                 | 55 W                                 | 30 W                                 | 111150741            | 60 W                                 | 35 W                                 | 35 W                                 |  |

| TNY5075K             | 75 W                                 | 70 W                                 | 45 W                                 | TNVF07FV             | 75 \\                                | 70 14/                               | 45.74                                |  |

| TNY5075V             | 75 W                                 | 70 W                                 | 40 W                                 | TNY5075V             | 75 W                                 | 70 W                                 | 45 W                                 |  |

|                      |                                      |                                      |                                      | TNY5075E             | 120 W                                | 105 W                                | 70 W                                 |  |

|                      |                                      |                                      |                                      | TNY5076E             | 150 W                                | 140 W                                | 95 W                                 |  |

|                      |                                      |                                      |                                      | TNY5077E             | 190 W                                | 175 W                                | 120 W                                |  |

Table 2. Output Power Table.

Notes:

- 1. The power table 2 represents the maximum practical continuous output power based on the following assumptions: The power table 2 represents the maximum practical continuous output power based on the following assua. 12 V output.

Schottky output diode.

130 V reflected voltage (V<sub>oR</sub>) and 85% efficiency.

A 100 VDC minimum DC bus voltage for 85-265 VAC and 300 VDC bus voltage for 230 VAC.

Sufficient heatsinking to keep device temperature ≤110 °C.

Power levels shown for the V package device assume 19.4 cm 2 of 610 g/m 2 copper heatsink area.

Open frame design operating in a +50 °C ambient temperature.

Minimum peak power capability.

Packages: E: eSIP-7C, V: eDIP-12B, K: eSOP-12B.

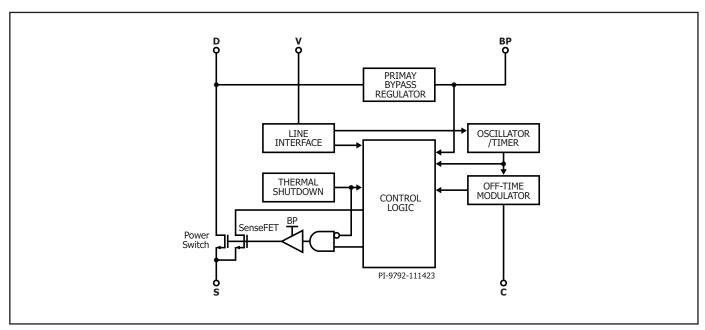

Figure 3. Functional Block Diagram.

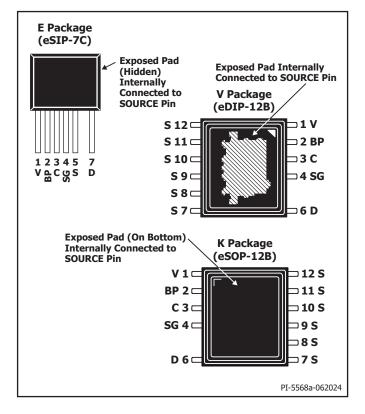

#### **Pin Functional Description**

### DRAIN (D) Pin

Power switch drain connection.

#### **SOURCE (S) Pin**

These pin(s) are the power switch source connection. Also ground reference for BYPASS pin.

#### **BYPASS (BP) Pin**

The connection point for an external bypass capacitor for the controller supply.

#### **VOLTAGE MONITOR (V) Pin**

Pin connected to the AC or DC side of the input bridge for detecting undervoltage and overvoltage conditions at the power supply input. This pin should be tied to SOURCE pin to disable UV/OV protection.

#### **CONTROL (C) Pin**

Feedback control current input pin.

#### **SIGNAL GROUND (SG) Pin**

SG pin must be connected to Source.

Figure 4. Pin Configuration (Top View).

#### **TinySwitch-5 Functional Description**

The TinySwitch<sup>™</sup>-5 IC is an integrated switched mode power supply IC that monitors an analog feedback current at the Control input which is then used to modulate the variable frequency variable current control algorithm.

The TinySwitch-5 flyback controller can operate in continuous conduction mode (CCM) or discontinuous conduction mode (DCM). The controller consists of a frequency jitter oscillator, a current limit controller, 5 V regulator on the BYPASS pin, BYPASS undervoltage and overvoltage detection circuit, an input line sensing circuit, over-temperature protection, leading edge blanking, and a silicon MOSFET power switch.

#### **BYPASS Pin Regulator**

The BYPASS pin has an internal regulator that charges the BYPASS pin capacitor to  $V_{\rm BP}$  by drawing current from the DRAIN pin whenever the power switch is off. The BYPASS pin is the internal supply voltage node. When the power switch is on, the device operates from the energy stored in the BYPASS pin capacitor.

In addition, a shunt regulator clamps the BYPASS pin voltage to  $V_{\text{SHUNT}}$  when current is provided to the BYPASS pin through an external resistor. This allows the TinySwitch-5 IC to be powered externally through a bias winding, decreasing the no-load consumption to less than 30 mW in a 5 V output design.

#### **Bypass Undervoltage Threshold**

The BYPASS pin undervoltage circuitry disables the power switch when the BYPASS pin voltage drops below  $\sim\!\!4.5$  V (V  $_{BP}$  – V  $_{BP(H)}$ ) in steady-state operation. Once the BYPASS pin voltage falls below this threshold, it must rise to V  $_{BP}$  to re-enable turn-on of the power switch.

#### **Bypass Output Overvoltage Function**

The BYPASS pin has an auto-restart OV protection feature. A Zener diode in parallel with the resistor in series with the BYPASS pin capacitor is typically used to detect an overvoltage on the bias winding and activate the protection mechanism. In the event that the current into the BYPASS pin exceeds  $\mathbf{I}_{\text{SD}}$ , the device will disable switching.

#### **Over-Temperature Protection**

The thermal shutdown circuitry senses the power switch temperature. The threshold is set to  $T_{\rm sn}$  with a hysteretic response.

Hysteresis response: If the die temperature rises above the threshold, the power switch is disabled and remains disabled until the die temperature falls by  $T_{\text{SD(H)}}$  at which point switching is re-enabled. A large amount of hysteresis is provided to prevent over-heating of the PCB due to a continuous fault condition.

#### **Off-Time Modulator**

The off-time modulator converts an analog feedback current to off-time duration, which is proportional to the feedback current. This algorithm produces longer off-time as the output load reduces.

At the end, of the off-time cycle, the off-time modulator initiates the on-cycle request to turn-on the integrated power switch.

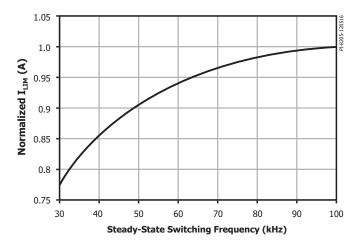

#### **Current Limit Operation**

The current limit threshold is proportional to the time between the termination of the previous switching cycle (power switch turns off) and the next switching request.

This characteristic produces a current limit that increases as the switching frequency (load) increases as shown in Figure 5.

At high load, switching cycles have a maximum current that approaches 100%  $I_{\text{Lim}}$ . This gradually reduces to 30% of the full current limit as load decreases. Once 30% current limit is reached, there is no further reduction in current limit (since this is low enough to avoid audible noise). The time between switching cycles will continue to increase as load reduces.

Figure 5. Normalized Current Limit vs Frequency.

#### **Jitter**

The normalized current limit is modulated between 100% and 94.5% at a modulation frequency of  $f_{\scriptscriptstyle M}.$

#### **SOA Protection**

After two consecutive cycles where the 110%  $I_{\text{LIM}}$  (100%  $I_{\text{LIM}}$  is  $I_{\text{LIM}}$  at 100 kHz) is reached between  $t_{\text{LEB}}$  and  $t_{\text{SOA}}$ , the controller will interrupt switching for approximately  $\sim\!\!20~\mu\text{s}$ , which is equivalent to approximately 3 cycles at maximum 150 kHz switching frequency. This provides sufficient time for the transformer to reset when delivering power to large capacitive loads without extending the start-up time.

#### **Input Line Voltage Monitoring**

The VOLTAGE MONITOR (V) pin is used for input undervoltage and overvoltage sensing and protection.

An 8  $M\Omega$  resistor is tied between the high-voltage DC bulk capacitor after the bridge (or to the AC side of the bridge rectifier along with suitable diode rectification for fast AC reset) and the VOLTAGE MONITOR pin to enable this functionality. This function can be disabled by shorting the VOLTAGE MONITOR pin to the SOURCE pin.

At power-up, after the bypass (BP) capacitor is charged and the  $\rm I_{LIM}$  state is set, and (prior to switching) the state of the VOLTAGE MONITOR pin current is checked to confirm that it is above the brown-in ( $\rm I_{UV+}$ ) and below the overvoltage shutdown thresholds ( $\rm I_{OV+}$ ).

In normal operation, if the VOLTAGE MONITOR pin current falls below the brown-out threshold ( $I_{\text{UV}}$ ) and remains below brown-out for longer than  $t_{\text{UV}}$ , switching is interrupted. Once the VOLTAGE MONITOR pin current is above the brown-in threshold (IUV+), the controller initiates a soft start.

During normal operation, if the VOLTAGE MONITOR pin current increases above the overvoltage threshold  $(I_{\text{Ov+}})$  for longer than  $t_{\text{Ov+}}$ , switching is interrupted. Switching will intiate a soft start once the VOLTAGE MONITOR pin current falls below  $(I_{\text{Ov}})$ .

#### **Maximum On-Time Extension**

On-time extension keeps the cycle on until current limit is reached. If current limit is not reached by  $t_{\text{ONEXT(MAX)}} = 15~\mu\text{s}$ , the controller terminates the switching cycle.

This feature reduces the minimum input voltage required to maintain regulation, extending hold-up time and minimizing the size of the bulk capacitor required.

### **Maximum Switching Frequency**

The maximum switching frequency of the controller is f<sub>osc</sub>.

#### **Minimum Off-Time**

The off-time modulator initiates a cycle request to turn ON the integrated power MOSFET switch. The maximum frequency of off-time modulator requests is limited by a minimum cycle off-time of  $t_{\text{OFF(MIN)}}.$  This ensures that there is sufficient reset time after the integrated switch conduction time for the transformer to deliver energy to the load.

#### **Maximum Duty Cycle**

The power MOSFET is turned off when the current ramps up to the current limit or when the  $t_{\text{ONEXT(MAX)}}$  limit is reached.

The controller monitors the power MOSFET on-time  $t_{\text{MOSFET(ON)}}$  and measures the timer  $t_{\text{DC(MAX)}} = \text{DC}_{\text{MAX}}/f_{\text{OSC}}$  from when the MOSFET turns on. If:

$t_{\text{MOSFET(ON)}} \geq t_{\text{DC(MAX)}'}$  the off-time modulation starts after the MOSFET is turned off.

$t_{\text{MOSFET(ON)}} < t_{\text{DC(MAX)}}$  the off-time modulation starts after  $t_{\text{DC(MAX)}}$  timer ends.

#### **Frequency Soft-Start**

At start-up, the controller linearly ramps the switching frequency up from  $f_{\text{SW(STARTUP)}}$  over the  $t_{\text{SOFT}}$  time period.

If the control pin current  $I_c$  rises above the  $I_{\rm C(TH)}$  threshold within the  $t_{\rm SOFT}$  time period, the frequency ramp is immediately aborted and the controller is permitted to go full frequency. This allows the controller to maintain regulation in the event of a sudden transient loading soon after regulation is achieved.

In the event of a short-circuit or overload at start-up, the controller moves into auto-restart (AR) mode if the control current  $I_{\rm c}$  does not rise above the  $I_{\rm CITH}$  threshold before the expiration of the  $t_{\rm AR}$  time.

### **Application Examples**

Figure 6. Schematic of RDR-1016 26.5 W, Dual Output Power Supply, 12 V / 2 A and 5 V / 500 mA using TNY5073K.

### A High Efficiency, 27 W Dual Output Power Supply (TinySwitch-5)

The circuit shown in Figure 6 delivers 27 W (12 V at 2 A and 5 V a 500 mA) from 85 VAC to 265 VAC input using TNY5073K.

The supply features line undervoltage lockout, line overvoltage protection, primary sensed output overvoltage auto-restart protection, output short-circuit protection, high 115 VAC full load efficiency (>86%), high 230 VAC full load efficiency (>87%), high average efficiency (>85.5%) and low no-load input power consumption (<50 mW at 230 VAC). Output regulation is accomplished using an optocoupler and a shunt regulator (TL431) feedback.

The input fuse F1 provides protection against excess input current resulting from catastrophic failure of any components in the power supply. The bridge rectifier BR2 rectifies the AC input supply. Capacitors C2 and C19 filter the rectified AC input, and together with inductor L4, form a pi-filter to attenuate differential mode EMI. The X capacitor C1 also helps to reduce differential mode EMI. The Y capacitor C7, connected between the power supply output and input, and reduces common mode EMI. Additionally, the TinySwitch-5 frequency jitter feature reduces EMI. One end of the transformer primary is connected to the rectified DC bus; the other is connected to the drain terminal of the power switch inside the TinySwitch-5 IC (U4).

Line undervoltage and overvoltage thresholds are determined by the current supplied by resistors R1 and R2 to the V pin.

A RCDZ clamp, consisting of diode D1, resistors R3 and R4, capacitor C3, and Zener VR1, limits the peak drain voltage of U4 at the moment the switch inside U4 turns off. The clamp helps to dissipate the energy stored in the leakage reactance of transformer T1.

The TinySwitch-5 IC is self-starting, using an internal high-voltage current source to charge the primary BYPASS pin capacitor (C17) when AC is first applied. An optional ferrite bead (L5) was used to increase noise immunity. During normal operation, the IC primary controller is powered from a bias winding on the transformer T1. Output of this bias winding is rectified by diode D2 and filtered by capacitor C4. Resistor R17 limits the current being supplied to the TinySwitch-5 IC (U4). Resistor R17 feeds current into the BP pin, inhibiting the internal high-voltage current source that normally maintains the BP pin capacitor voltage (C17) during the internal MOSFET off-time. This design reduces no-load consumption to less than 50 mW at 230 VAC.

Primary sensed OVP can be achieved by connecting a series combination of a Zener diode (VR2), a current limiting resistor (R5), and a blocking diode (D3) from the bias voltage supply to the BYPASS pin. In the event of overvoltage on any output, the increased voltage at the output of the bias winding causes the Zener diode (VR2) to conduct, increasing current into the BP pin. Once the current exceeds current threshold ( $I_{SD}$ ), the TinySwitch-5 will stop switching, and auto-restart will occur until V<sub>OUT</sub> is within regulation.

Output rectification for the 12 V output is provided by the secondary rectifier diode D4, while the 5V output rectification is accomplished by

secondary rectifier diode D5. An RC snubber network, consisting of R8 and C8 for D4 and R9 and C11 for D5, damps high frequency ringing across the secondary rectifier diodes, which results from leakage inductance in the transformer windings and the secondary trace capacitance.

Very low ESR capacitors, C9 and C12, provide filtering for their respective outputs. Ferrite beads L2 and L3, along with output capacitors C10 and C13, form a low-pass filter that helps reduce output ripple for both 12 V and 5 V outputs.

In the feedback circuit, the output voltages are sensed via the resistor divider R10, R11, and R15. These voltages are regulated to achieve 2.495 V on the TL431 REF pin. The feedback current ratio between the 12 V and 5 V outputs is approximately 1:1, ensuring better output regulation and good cross-regulation. As the cathode voltage changes, the current through the optocoupler LED and transistor within U2 changes. R12, R14 and C15 provide stable operation, while resistor R16 ensures minimum bias to U3. The bias winding voltage was tuned to approximately 10 V at no-load, high line to reduce no-load input power.

Typically, the feedback current into the CONTROL pin at high-line is around 250  $\mu\text{A}.$  This current is sourced from both the bias winding (voltage across C4) and directly from the output, representing a load on the power supply's output. To minimize dissipation from the bias winding under no-load conditions, the number of bias winding turns and the value of C4 were adjusted to achieve a minimum voltage of approximately 10 V across C4. This is the minimum required to keep the optocoupler biased and the output in regulation.

To further minimize dissipation in the secondary-side feedback circuit, a high CTR (300-600%) optocoupler was used. This reduces the secondary-side opto-LED current from around 250  $\mu\text{A}$  to less than 90  $\mu\text{A}$ , thereby reducing the effective load on the output. Additionally, the standard 2.5 V TL431 voltage reference can be replaced with the 1.24 V LMV431, reducing the supply current requirement of this component from 1 mA to 100  $\mu\text{A}$ .

A heat spreader in the form of a PCB copper plane is required to keep the TinySwitch-5 and secondary rectifier diode device below 110  $^{\circ}\text{C}$  when operating.

### **Key Application Design Considerations**

#### **Power Table**

The output power table in the data sheet (Table 2) represents the maximum practical continuous output power that can be obtained under the following conditions:

- The minimum DC input voltage is 85 V or higher for 85 VAC input, and 220 V or higher for 230 VAC input. The input capacitor voltage should be sized to meet these criteria for AC input designs.

- Efficiency assumptions depend on input voltage range. Universal input voltage or low line input assumes efficiency >85% increasing to >89% for a high line input. The assumed efficiency is based on the lowest voltage of the input range.

- 3. Transformer primary inductance tolerance of  $\pm 10\%$ .

- 4. Reflected output voltage (VOR) is set to maintain  $K_{\rm p} > 0.4$  at a minimum input voltage to provide the maximum power. At high line nominal, it recommended to designed  $K_{\rm p}$  between 1 and 1.1 to increase efficiency.

- Use low forward voltage drop (V<sub>F</sub>) Schottky diode for efficiency improvements.

- The part is board-mounted with SOURCE pins soldered to a sufficient area of copper and/or a heatsink to maintain the device temperature at or below 110 °C at the required highest ambient temperature.

- An ambient temperature of 50 °C for open frame designs and 40 °C for sealed adapters is assumed.

- 8. A unique feature of TinySwitch-5 IC is that a designer can set the operating switching frequency between 25 kHz to 142 kHz depending on the transformer design. One effective way to lower U4 temperature is to design the transformer to operate at a lower switching frequency, with a good starting point being 66 kHz. If a smaller size transformer is needed, the operating switching frequency can be increased to 130 kHz.

#### **Overvoltage Protection**

The output overvoltage protection provided by TinySwitch-5 uses an internal protection that is triggered by a threshold current ( $I_{\text{SD}}$ ) into the BYPASS pin. In addition to an internal filter, the BYPASS pin capacitor forms an external filter, providing noise immunity and preventing inadvertent triggering. To ensure the bypass capacitor is effective as a high-frequency filter, it should be placed as close as possible to the SGND and BYPASS pins of the device.

The primary sensed output OVP function can be achieved by connecting a series combination of a Zener diode (VR2), a resistor (R5), and a blocking diode (D3) from the rectified and filtered bias winding voltage supply to the BYPASS pin. The rectified and filtered bias winding output voltage may be higher than expected (up to 1.5X or 2X the desired value) due to poor coupling of the bias winding with the output winding and the resulting ringing on the bias winding voltage waveform. It is therefore recommended to measure the rectified bias winding voltage, at the lowest input voltage and highest load on the output. This measured voltage should be used to select the components required to achieve primary sensed OVP.

A Zener diode with a clamping voltage approximately 6 V lower than the bias winding rectified voltage at which OVP is expected to be triggered should be selected. A forward voltage drop of 1 V can be assumed for the blocking diode, and a small signal standard recovery diode is recommended. The blocking diode prevents any reverse current from discharging the bias capacitor during start-up. Finally, the value of the series resistor should be calculated to ensure that a current higher than  $\rm I_{5D}$  flows into the PRIMARY BYPASS pin during an output overvoltage event.

#### **Reducing No-load Consumption.**

The TinySwitch-5 IC starts in self-powered mode, drawing energy from the BYPASS pin capacitor, which is charged from an internal current source. Once the TinySwitch-5 IC begins switching, a bias winding is required to provide supply current to the BYPASS pin. This bias winding supply enables power supplies to achieve low no-load power consumption. The value of resistor  $R_{\mbox{\scriptsize BIAS}}$  should be adjusted to achieve the lowest no-load input power.

Additional techniques to further reduce no-load consumption include:

- 1. Using a low value primary clamp capacitor (C<sub>PRI SNUB</sub>).

- 2. Employing a Schottky or ultrafast diode for the bias supply rectifier ( $D_{RIAC}$ ).

- Employing high Current Transfer Ratio optocoupler with a CTR of 300-600% (OPTO)

- 4. Selecting a low ESR capacitor for the bias supply filter capacitor  $(C_{\text{BIAS}})$ .

- Selecting low ESR for input bulk capacitor (C<sub>BULK</sub>) and output filter capacitor (C<sub>OUT</sub>).

- Utilizing a low value secondary rectifier diode RC snubber capacitor (C<sub>SEC\_SNUB</sub>).

Applying tape between primary winding layers and multi-layer

- Applying tape between primary winding layers and multi-layer tapes between primary and secondary windings to reduce inter-winding capacitance.

#### **Component Selection**

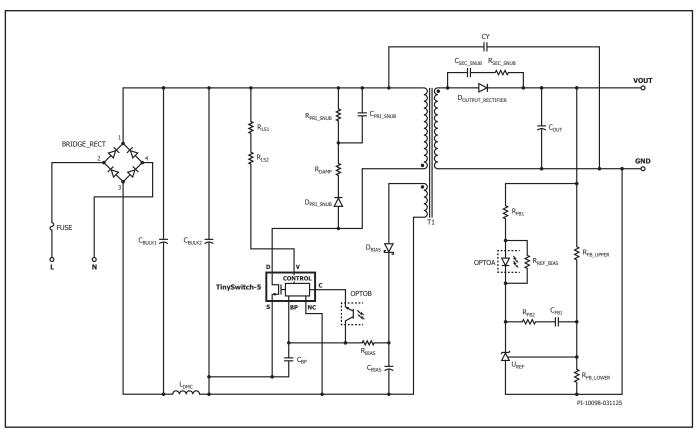

Figure 7 shows the key external components required for a practical single output TinySwitch-5 design.

Figure 7. Typical TinySwitch-5 Flyback Power Supply Single-output design.

#### BYPASS Pin Capacitor (C<sub>RD</sub>)

A capacitor connected from the BYPASS pin (BP) of the TinySwitch-5 IC to SGND provides decoupling for the primary controller. A 0.47  $\mu F$  capacitor may be used. While electrolytic capacitors are an option, surface mount multi-layer ceramic capacitors are often preferred for double-sided boards as they can be placed close to the IC. Their small size also makes them ideal for compact power supplies. At least 10 V, 0805 or larger size X5R or X7R dielectric capacitors are recommended to ensure minimum capacitance requirements are met. Note that ceramic capacitor type designations, such as X7R and X5R, can vary in voltage coefficients across different manufacturers or product families. It is advisable to review capacitor data sheets to ensure the selected capacitor does not experience more than a 20% drop in capacitance at 5 V. Avoid using Y5U or Z5U / 0603 rated MLCCs, as they have poor voltage and temperature coefficient characteristics.

#### V Pin Line Sense Resistors ( $R_{LS1}$ and $R_{LS2}$ )

Resistors connected from the V pin to the DC bus enable input voltage sensing for line undervoltage and overvoltage protection. For a typical universal input application, a total resistor value of 8 M $\Omega$  is recommended. For high line input, it is advisable to use two 0.25 W SMD 1206 resistors or leaded resistors in series, each with a value of 4 M $\Omega$ .

Connecting the V pin to SOURCE disables the line sensing function. It is not recommended to leave the V pin floating.

# Primary Clamp (D<sub>PRI\_SNUB</sub>, R<sub>DAMP</sub>, R<sub>PRI\_SNUB</sub>, C<sub>PRI\_SNUB</sub>)

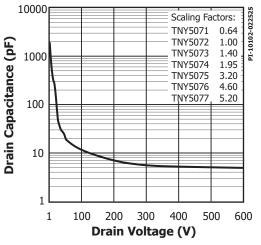

Refer to Figure 7. An RRCD clamp is a commonly used clamp in low-power power supplies. For higher power designs, a Zener clamp or RRCD + Zener clamp can be used to increase efficiency. It is advisable to limit the peak drain voltage to 90% of the device absolute DRAIN voltage rating under worst-case conditions (maximum input voltage, maximum overload power or output short-circuit).

The clamp diode ( $D_{PRL\_SNUB}$ ) must be a standard recovery glass-passivated type or a fast recovery diode with a reverse recovery time of less than 500 ns. Using standard recovery glass passivated diodes allows recovery of some of the clamped energy in each switching cycle, improving light-load and average efficiency. The diode conducts momentarily each time the MOSFET inside TinySwitch-5 turns off, transferring the stored energy from the leakage reactance and the clamp capacitor  $C_{PRI\_SNUB}$  to the output

Resistor  $R_{\text{DAMP}}$  in the series path, provides damping preventing excessive ringing due to resonance between the leakage inductance and the MOSFET switch output capacitance  $C_{\text{OSS}}$ . Resistor  $R_{\text{PRL\_SNUB}}$  bleeds-off energy stored in the capacitor  $C_{\text{PRL\_SNUB}}$ . Power supplies using different TinySwitch-5 devices in the family will have different peak primary current, leakage inductances and therefore leakage energy. Capacitor  $C_{\text{PRL\_SNUB}}$  and resistor  $R_{\text{PRI\_SNUB}}$  and  $R_{\text{DAMP}}$  must therefore be optimized for each design.

As a general rule it is advisable to minimize the value of capacitor  $C_{\text{PRI\_SNUB}}$  and maximize the value for  $R_{\text{PRI\_SNUB}}$  and  $R_{\text{DAMP'}}$  while ensuring the MOSFET DRAIN voltage remains below 90% of its absolute maximum limit at the highest input voltage and maximum load. The value of  $R_{\text{DAMP}}$  should be large enough to damp the ringing within the required time. However, as the value of  $R_{\text{DAMP}}$  increases the DRAIN peak voltage and its power dissipation also increase. Therefore, care must be taken to keep the DRAIN voltage below 90% of its maximum absolute limit. The recommended range for  $R_{\text{DAMP}}$  is 47  $\Omega$  to 100  $\Omega$ . While the recommended range for  $R_{\text{PRI\_SNUB}}$  is 100  $k\Omega$  to 470  $k\Omega$ .

Using a disc ceramic capacitor with dielectric such as Z5U in the clamp circuit for  $C_{\tt PRI\_SNUB}$  may generate audible noise, therefore a polyester film type or a ceramic capacitor with X7R as a dielectric, 1 kV rating, 1206 size is commonly used. The recommended range for  $C_{\tt PRI\_SNUB}$  is 470 pF to 1 nF.

# Bias Winding and External Bias Supply Circuit ( $D_{\text{BIAS}'}$ $C_{\text{BIAS}'}$ $R_{\text{BIAS}}$ )

The internal primary bypass regulator connected from the DRAIN pin to the BYPASS pin of the TinySwitch-5 IC charges the capacitor  $C_{\mbox{\footnotesize BP}}$  connected to the BYPASS pin to achieve start-up. A bias winding should be provided on the transformer with a suitable rectifier and filter capacitor to create a bias supply that can supply at least 1.5 mA of current to the BYPASS pin and C pin.

A bias voltage of 12 V is recommended at full load. Higher voltage will increase no-load input power. To reduce no-load consumption and improve standby input efficiency, ultrafast or Schottky diodes are recommended for the bias winding rectifier. The turns ratio for the bias winding should be selected such that 10 V is developed across the bias winding at the lowest rated output voltage of the power supply under the lowest load condition. If the voltage is lower than this, no-load input power will increase.

The bias current from the external circuit should be set to slightly higher than  $I_{\rm S1}$  of 258  $\mu A$  to achieve the lowest no-load power consumption when operating the power supply at 230 VAC input. This can be achieved by fine tuning the value of  $R_{\rm BIAS}$  resistor. A glass-passivated standard recovery rectifier diode with low junction capacitance is recommended to avoid the snappy recovery typically seen with fast or ultrafast diodes, which can lead to higher radiated FMI.

An aluminum low ESR electrolytic capacitor of at least 47  $\mu$ F and 25 V rating is recommended for the bias filter capacitor  $C_{\text{BIAS}}$ . A 47  $\mu$ F low ESR electrolytic capacitor will help to improve the no-load input power and standby input power efficiency. The use of ceramic surface mount capacitors is not recommended, as they can cause audible noise due to the piezoelectric effect in their mechanical structure.

To achieve minimum no-load input power and high full load efficiency, the resistor  $R_{\mbox{\scriptsize BIAS}}$  should be selected such that the current through this resistor is higher than the required BYPASS pin current.

## Secondary Output Rectifier Diode (D<sub>OUTPUT\_RECTIFIER</sub>)

The output diode is selected based on peak inverse voltage, output current, and thermal conditions in the application, including heatsinking and air circulation. The higher  $DC_{MAX}$  of the TinySwitch-5 IC, combined with an appropriate transformer turns ratio, allows the use of an 80 V Schottky diode for higher efficiency at output voltages up to 15 V.

Considerations for selecting an output rectifier diode:

- Ensure the reverse voltage rating (V<sub>R</sub>) is at least 1.25 times the peak inverse voltage (PIV).

- Select a diode with a current rating (I<sub>D</sub>) that is at least twice the output current (I<sub>OUT</sub>).

#### Output Filter Capacitance (Cout)

A low ESR electrolytic capacitors is one of the key requirements in smoothing output ripple voltage. Other parameters to be considered are the RMS ripple current rating, DC working voltage and ESR. The actual capacitance value is of less importance.

Considerations for Selection of Output Capacitor:

- Ensure the capacitor ripple is specified @ 105  $^{\circ}$ C, 100 kHz must be larger than the expected ripple current (IS\_{RIPPLE}).

- Use a low ESR (Equivalent Series Resistance) electrolytic capacitor to minimize output switching ripple voltage, which is calculated using V<sub>RIPPLE</sub> = IS<sub>RIPPLE</sub> x ESR.

- Select a capacitor with a voltage rating such that the rated voltage is at least 1.25 times the output voltage (V<sub>OLT</sub>).

### Output Post Filter Components ( $L_{p_F}$ and $C_{p_F}$ ):

A post filter ( $L_{PF}$  and  $C_{PF}$ ) can be added to reduce high frequency switching noise and ripple.

Considerations for Adding a Post Filter:

- The inductor (L<sub>PF</sub>) should have an inductance value in the range of 1 μH to 3.3 μH and a current rating that exceeds the peak output current.

- The capacitor (C<sub>PF</sub>) should have a capacitance value in the range of 100 μF to 330 μF and a voltage rating that is at least 1.25 times the output voltage (V<sub>OLIT</sub>).

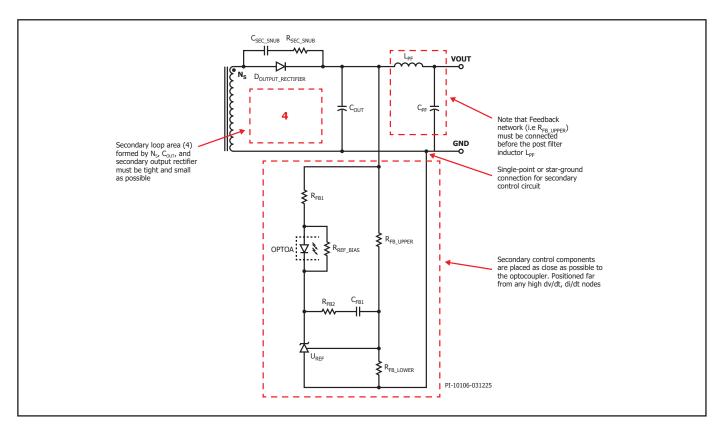

- If a post filter is used, ensure that the output voltage sense resistor and optocoupler are connected before the post filter inductor. See Figure 9.

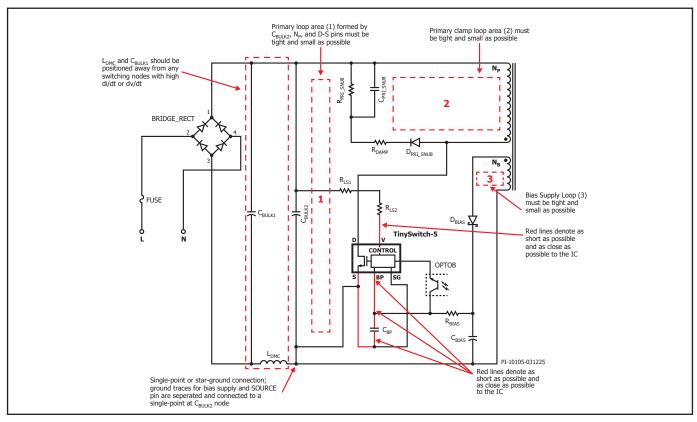

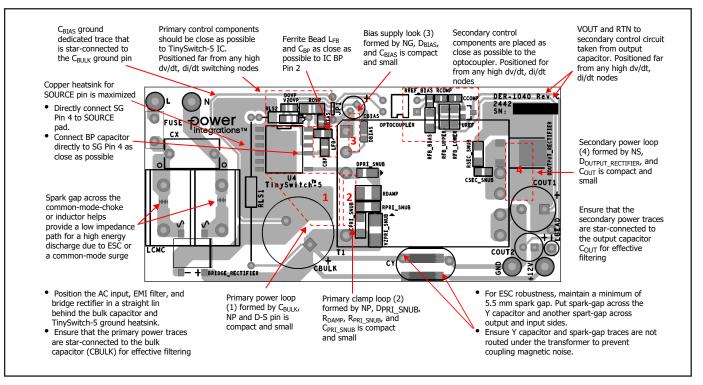

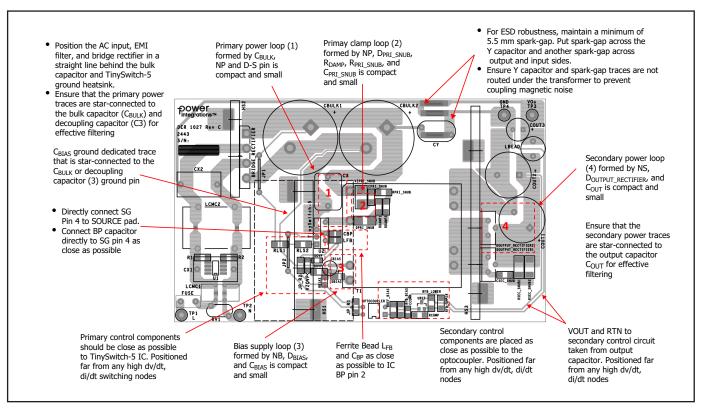

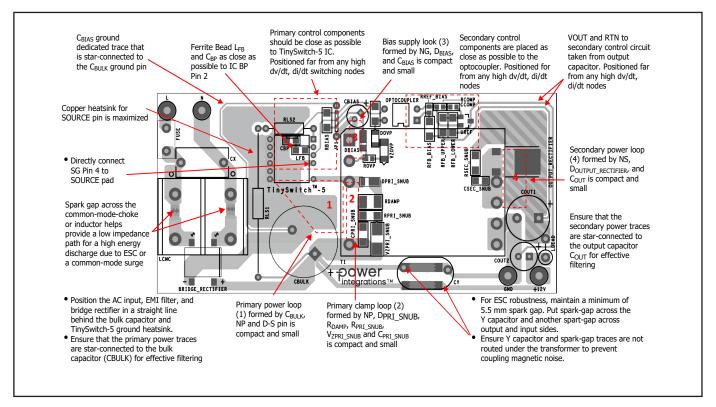

#### **Recommendations for Circuit Board Layout**

For this section refer to Figures 8 to 12

#### **Single-Point Grounding**

Use a single-point ground connection from the input filter capacitor to the area of copper connected to the SOURCE pin. The  $C_{\text{BIAS}}$  ground should have a dedicated trace that is star-connected to the input filter capacitor ground pin.

#### **Bypass Capacitors**

The BYPASS pin decoupling capacitor ( $C_{\rm gp}$ ) must be located directly adjacent to the BYPASS and SOURCE pins. Ensure the connections should be routed via short traces.

#### **Critical Loop Area**

Circuits with high dv/dt or di/dt should be kept as small as possible. Minimize the area of the primary loop that connects the input filter capacitor, transformer primary, and IC. Similarly, reduce the area of the loop connecting the secondary winding, output rectifier diode, and output filter capacitor.

Ensure that no loop area is placed inside another loop to minimize crosstalk between circuits.

#### **Drain Node**

The drain switching node is the dominant noise generator. Therefore, components connected to the drain node should be placed close to the IC and away from sensitive primary control circuits. The clamp circuit components should be physically located away from the BYPASS pin, and the trace width and length in this circuit should be minimized.

#### **Power Trace Routing**

Current will flow through the path of least resistance. Even if the trace is connected to the capacitors, there is a possibility that the current may bypass them, rendering the capacitors ineffective. For effective filtering and noise immunity, it is recommended that power signal traces be star-connected to the capacitor's pads.

#### **Primary Clamp Circuit**

A clamp is used to limit the peak voltage on the DRAIN pin during turn-off. This can be achieved by using an R2CD or R2CDZ clamp across the primary winding. To reduce EMI, minimize the loop area between the clamp components, the transformer, and the IC.

#### Y Capacitor

The Y capacitor should be placed directly from the positive terminal of the primary input filter capacitor to the output positive or return terminal of the transformer secondary. This placement will route high-magnitude common mode surge currents away from the IC.

If an input pi EMI filter ( $C_{\text{BULK1}}$ ,  $L_{\text{DMC}}$ ,  $C_{\text{BULK2}}$ ) is used, the inductor should be placed between the negative terminals of the input filter capacitors.

#### **ESD Immunity**

Sufficient clearance should be maintained between the primary-side and secondary-side circuits to ensure compliance with ESD and hi-pot isolation requirements. The spark gap should be placed between the output return and/or positive terminals and one of the AC inputs (after the fuse). In this configuration, a 6.4 mm spark gap (5.5 mm is acceptable, depending on customer requirements) is sufficient to meet the creepage and clearance requirements of most safety standards for a universal input power supply. For effective ESD immunity, the spark gap spacing should be the closest distance between the primary and secondary sections.

A spark gap across the common-mode choke or inductor provides a low impedance path for high-energy discharges due to ESD or common-mode surges.

#### **Secondary Rectifier Diode**

For optimal performance, the loop area connecting the secondary winding, secondary rectifier diode, and output filter capacitor should be minimized. When using SMD diodes, ensure sufficient copper area at the terminals of the secondary rectifier diode for heat dissipation. A heatsink may be required for the secondary diode.

#### **Thermal Considerations**

The SOURCE pin is internally connected to the IC lead frame and serves as the main path for heat removal in V and K packages. Therefore, the SOURCE pin should be connected to a copper area underneath the IC, functioning as both a single-point ground and a heatsink. Since this area is connected to the quiet source node, it can be maximized for effective heat dissipation without causing EMI issues. K packages feature an exposed pad at the bottom of the IC, which should be soldered to the SOURCE copper heatsink to further reduce the IC temperature.

For E packages, the exposed pad at the back of the IC is used to attach a heatsink. A heatsink is necessary to ensure the IC operates safely below the absolute maximum junction temperature limit.

Sufficient copper area or a heatsink should be provided on the board to maintain the IC temperature safely below absolute maximum limits. It is recommended that the copper area or heatsink keeps the IC temperature below 110°C when operating the power supply at full rated load, the lowest rated input AC supply voltage, and system's maximum operating ambient temperature. Further de-rating can be applied as needed.

Figure 8. Typical Schematic of TinySwitch-5 Primary-Side Showing Critical Loops Areas, Critical Component Traces, and Single-Point or Star Grounding.

Figure 9. Typical Schematic of TinySwitch-5 Secondary-Side Showing Critical Loops Areas, Critical Component Traces and Single-Point or Star Grounding. Optional Post Filter LC included.

#### **Layout Example**

Figure 10. TOP and BOTTOM Sides – Ideal Layout Example Showing Tight Loop Areas for Circuit with High dv/dt or di/dt, Component Placement and Spark-Gap Location for TinySwitch-5 K-package.

Figure 11. TOP and BOTTOM Sides – Ideal Layout Example Showing Tight Loop Areas for Circuit with High dv/dt or di/dt, Component Placement and Spark-Gap Location for TinySwitch-5 E-package.

Figure 12. TOP and BOTTOM Sides – Ideal Layout Example Showing Tight Loop Areas for Circuit with High dv/dt or di/dt, Component Placement and Spark-Gap Location for TinySwitch-5 V-Package.

#### **Special Notes on PCB Layout**

- Ensure all loops are separated, with no loop inside another loop, to avoid ground impedance noise coupling.

- Minimize the surface area and length of high dv/dt nodes, such as the Drain, to reduce RFI (Radio Frequency Interference) generation.

- Avoid routing quiet signal traces, such as those for Y capacitors and feedback returns, near or across noisy nodes (high dv/dt or di/dt), such as the Drain, underneath the transformer belly, the switching side of any winding, or the output rectifier diode. This helps prevent capacitive or magnetic noise coupling.

#### **Recommendation for EMI Reduction**

- Ensure appropriate component placement and minimize loop areas of the primary and secondary power circuits to reduce radiated and conducted EMI. Aim for a compact loop area.

- Adding a small capacitor in parallel with the clamp diode on the primary side can help reduce radiated EMI.

- 3. A resistor in series with the bias winding can help reduce radiated FMT

- 4. Common mode chokes (CMC) are often required at the power supply input to attenuate common mode noise. Alternatively, shield windings on the transformer can achieve similar performance. Shield windings can also be used with common mode filter inductors at the input to improve conducted and radiated EMI margins.

- Adjusting the RC snubber component values of the secondary rectifier diode can help reduce high frequency radiated and conducted EMI.

- Use a pi-filter comprising differential inductors and capacitors in the input rectifier circuit to reduce low-frequency differential EMI.

- 7. Connecting a 1  $\mu F$  ceramic capacitor at the power supply output helps reduce radiated EMI.

### **Recommendation for Transformer Design**

The transformer design must ensure that the power supply delivers the rated power at the lowest input voltage. The lowest voltage on the rectified DC bus depends on the capacitance of the bulk capacitor used. It is recommended to use at least 2  $\mu\text{F/W}$  to maintain the DC bus voltage above 90 V, though 3  $\mu\text{F/W}$  provides the typical margin. The ripple on the DC bus should be measured to confirm the design calculations for transformer primary-winding inductance selection.

#### Reflected Output Voltage, VOR (V)

This parameter represents the secondary winding voltage during the diode conduction time, reflected to the primary through the transformer's turns ratio. The default value is 130 V, but VOR can be adjusted to achieve a design that adheres to design rules. For design optimization, consider the following factors:

- Higher VOR allows increased power delivery at VMIN, minimizing the value of the input capacitor and maximizing power delivery.

- Higher VOR reduces voltage stress on the output diodes, potentially allowing for a lower voltage rating and higher efficiency.

- Higher VOR increases leakage inductance which reduces power supply efficiency.

- Higher VOR increases peak and RMS current on the secondary side, potentially increasing secondary side copper and diode losses, thereby reducing efficiency.

It should be noted that there are exceptions to this guidance, especially for very high output currents where the VOR should be reduced to achieve the highest efficiency. For higher output voltages (above 15 V), a higher VOR should be employed to maintain an acceptable peak inverse voltage (PIV) across the output diode.

Optimal selection of the VOR value depends on the specific application and involves a compromise between the factors mentioned above.

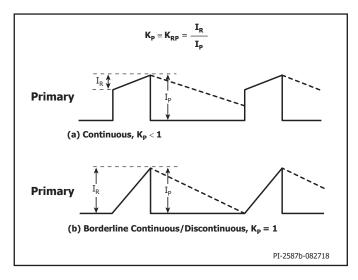

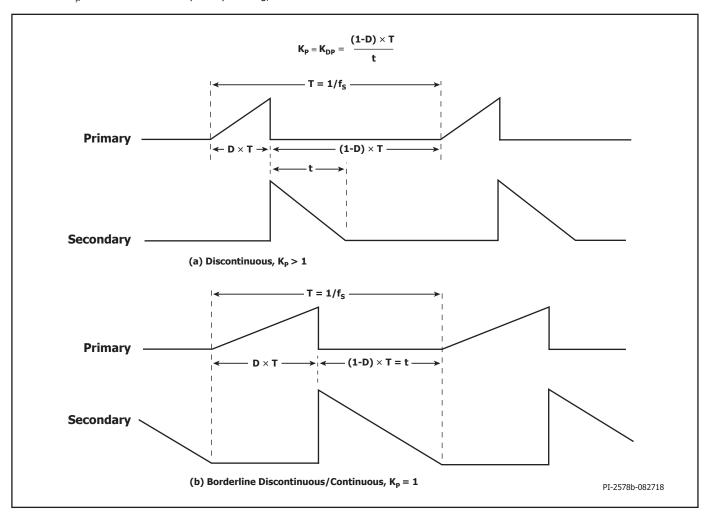

#### Ripple to Peak Current Ratio (K<sub>P</sub>)

A  $K_p$  below 1 indicates continuous-conduction mode, where  $K_p$  is the ratio of ripple current to peak primary current (Figure 13).

$$K_{\scriptscriptstyle P} \equiv K_{\scriptscriptstyle RP} = rac{I_{\scriptscriptstyle R}}{I_{\scriptscriptstyle D}}$$

A  $\rm K_p$  value higher than 1 indicates discontinuous conduction mode. In this case,  $\rm K_p$  is the ratio of primary switch off-time to secondary diode conduction time.

$$K_{\text{\tiny P}} \equiv K_{\text{\tiny DP}} = \frac{(1 \text{--}D) \times T}{t} = \frac{VOR \times (1 \text{--}D_{\text{\tiny MAX}})}{(V_{\text{\tiny MIN}} \text{--}V_{\text{\tiny DS}}) \times D_{\text{\tiny MAX}}}$$

It is recommended to use a  $K_{\rm p}$  close to 0.9 at the minimum expected DC bus voltage for most TinySwitch-5 designs. A  $K_{\rm p}$  value of less than 1 results in higher transformer efficiency by lowering the primary RMS current but leads to higher switching losses in the primary-side switch, resulting in a higher TinySwitch-5 IC temperature.

The PIXIs spreadsheet can be used to effectively optimize the selection of  $K_{\text{o}}$ , the inductance of the primary winding, the

transformer turns ratio, and the operating frequency while ensuring appropriate design margins.

Figure 13. Continuous Conduction Mode Current Waveform,  $K_p < 1$ .

Figure 14. Discontinuous Conduction Mode Current Waveform,  $K_p > 1$ .

#### Maximum Flux Density, B<sub>M</sub> (Gauss)

A maximum value of 3800 gauss at the peak device current limit is recommended to limit the peak flux density during start-up and under output short-circuit conditions. Under these conditions, the output voltage is low, and there is minimal reset of the transformer during the switch off-time. This allows the transformer flux density to staircase beyond the normal operating level. A value of 3800 gauss at the peak current limit of the selected device, combined with the built-in protection features of the TinySwitch-5 IC, provides sufficient margin to prevent core saturation under start-up or output short-circuit conditions

#### Transformer Primary Inductance, Lp

Once the lowest operating input voltage, switching frequency at full load, and required VOR are determined, the transformers primary inductance can be calculated. The PIXIs design spreadsheet can be used to assist in designing the transformer.

#### **Core Type**

The choice of a suitable core depends on the physical constraints of the power supply enclosure. It is recommended to use only low-loss cores to minimize thermal challenges.

#### Safety Margin, MARGIN (mm)

For designs that require safety isolation between primary and secondary but are not using triple insulated wire the width of the safety margin to be used on each side of the bobbin should be entered here. Typically for universal (85 – 265 VAC) input designs a total margin of 6.2 mm is required, and a value of 3.1 mm should be entered into the spreadsheet. For vertical bobbins, the margin may not be symmetrical; however, if a total margin of 6.2 mm is required then 3.1 mm would still be entered even if the physical margin were only present on one side of the bobbin. For designs using triple insulated wire it may still be necessary to enter a small margin to meet the required safety creepage distances. Typically, several bobbins exist for each core size, and each will have different mechanical spacing. Refer to the bobbin data sheet or seek guidance to determine what specific margin is required.

Margin reduces the available area for the windings, marginated construction may not be suitable for small core sizes. If after entering the margin more than 3 primary layers are required, it is suggested that either a larger core be selected or that the design is switched to a zero-margin approach using triple insulated wire.

#### Primary Layers, L

Primary layers should be in the range of 1 to 3, with the lowest number that meets the primary current density limit (CMA) being preferred. A value of ≥200 Circular-mils/Amp can be used as a starting point for most designs, though higher values may be required due to thermal constraints. Designs with more than three layers are possible, but increased leakage inductance and the physical fit of the windings should be considered.

A split primary construction may be beneficial for designs where clamp dissipation due to leakage inductance is too high. In split primary construction, half of the primary winding is placed on either side of the secondary (and bias) winding in a sandwich arrangement. However, this arrangement can be disadvantageous for low power designs as it typically increases common mode noise and adds cost to the input filtering.

#### **Quick Design Checklist**

As with any power supply, the operation of all TinySwitch-5 designs should be verified on-the-bench to make sure that component limits are not exceeded under worst-case conditions. As a minimum, the following tests are strongly recommended:

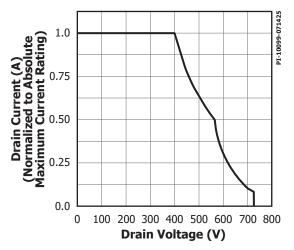

#### **Maximum Drain Voltage**

Verify that  $V_{\rm DS}$  of TinySwitch-5 and reverse voltage of the secondary rectifier diode do not exceed 90% of breakdown voltages at the highest input voltage and peak (overload) output power in normal operation and during start-up.

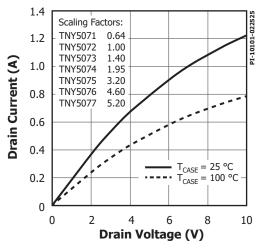

#### **Maximum Drain Current**

At maximum ambient temperature, maximum input voltage and peak output (overload) power. Review Drain current waveforms for any signs of transformer saturation or excessive leading-edge current spikes at start-up. Repeat tests under steady-state conditions and verify that the leading-edge current spike is below  $I_{\text{LIMIT}(\text{MIN})}$  at the end of  $t_{\text{LEB}\,(\text{MIN})}$ . Under all conditions, the maximum Drain current for the primary MOSFET should be below the specified absolute maximum ratings.

#### **Thermal Check**

At the specified maximum output power, minimum input voltage and maximum ambient temperature. Verify that temperature specification limits for the TinySwitch-5 IC, transformer, bridge rectifier, secondary rectifier Diode, and output capacitors are not exceeded. Enough thermal margin should be allowed for part-to-part variation of MOSFET  $R_{\text{DS(ON)}}.$  At low-line, maximum power, a maximum TinySwitch-5 IC temperature of 110 °C is recommended to allow for  $R_{\text{DS(ON)}}$  variation.

#### **Design Support**

Up-to-date information on design support can be found at the Power Integrations website: www.power.com

#### Absolute Maximum Ratings1,2

| TN<br>TN<br>TN              | Y5071 |              |

|-----------------------------|-------|--------------|

|                             | Y5076 |              |

|                             | Y5077 |              |

| BP Pin Voltage              |       | 0.3 to 6 V   |

| BP Pin Current              |       | 100 mA       |

| V Pin Voltage               |       | 0.3 V to 6 V |

| C Pin Voltage               |       | 0.3 V to 6 V |

| Storage Temperature         |       | 65 to 150 °C |

| Operating Junction Temperat |       |              |

| Ambient Temperature         |       | 40 to 105 °C |

| Maximum Lead Temperature    | 5     | 260 °C       |

#### Notes:

- 1. All voltages referenced to SOURCE and secondary GROUND,  $\rm T_{\scriptscriptstyle \Delta} = 25~^{\circ}C.$

- Maximum ratings specified may be applied one at a time without causing permanent damage to the product. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect product reliability.

- 3. Please refer to Figure 15 about maximum allowable voltage and current combinations.

- 4. Normally limited by internal circuitry.

- 5. 1/16 in. from case for up to 5 seconds.

#### **Thermal Resistance**

Thermal Resistance: E Pack

| E Package            |                     |

|----------------------|---------------------|

| $(\theta_{JA})$      | 105 °C/W1           |

| (θ <sub>IC</sub> )   | 2 °C/W <sup>2</sup> |

| V Package            |                     |

| $(\theta_{10})$      | 8 °C/W3, 58 °C/W4   |

| (θ <sub>1C</sub> )   | 2 °C/W²             |

| K Package            |                     |

| $(\theta_{1\Delta})$ | 5 °C/W3, 38 °C/W4   |

| $(\theta_{\rm IC})$  | 2 °C/W²             |

| 30                   |                     |

#### Notes:

- 1. Free standing with no heatsink.

- 2. Measured at the back surface of tab.

- Soldered (including exposed pad for K package) to typical application PCB with a heatsinking area of 0.36 sq. in. (232 mm²), 2 oz. (610 g/m²) copper clad.

- Soldered (including exposed pad for K package) to typical application PCB with a heatsinking area of 1 sq. in. (645 mm²), 2 oz. (610 g/m²) copper clad.

| Parameter                                                       | Symbol                      | $T_1 = -40$ °C to 125                                                                                                       | Conditions SOURCE = 0 V $T_{J} = -40 \text{ °C to } 125 \text{ °C}$ (Unless Otherwise Specified) |       |       | Max   | Units |

|-----------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| <b>Control Functions</b>                                        |                             |                                                                                                                             |                                                                                                  |       | l     | l     |       |

| Start-Up Off-Time                                               | T <sub>OFF(STARTUP)</sub>   | T <sub>J</sub> = 25 °C                                                                                                      |                                                                                                  |       | 30    | 45    | μS    |

| Maximum Operating<br>Frequency                                  | f <sub>osc</sub>            | T <sub>J</sub> = 25 °C                                                                                                      |                                                                                                  | 139   | 150   |       | kHz   |

| Jitter Modulation<br>Frequency                                  | f <sub>M</sub>              | $T_{_{\mathrm{J}}} = 25  ^{\circ}\mathrm{C}$<br>$f_{_{\mathrm{SW}}} = 150  \mathrm{kHz}$                                    |                                                                                                  |       | 0.22  |       | kHz   |

| Maximum Duty Cycle                                              | DC <sub>MAX</sub>           | T <sub>3</sub> = 25 °C                                                                                                      |                                                                                                  | 59    | 66    |       | %     |

| Maximum On-Time<br>Extension                                    | T <sub>ONEXT(MAX)</sub>     | T <sub>J</sub> = 25 °C                                                                                                      |                                                                                                  | 12.5  | 15    |       | μS    |

| Minimum Off-Time                                                | T <sub>OFF(MIN)</sub>       | T <sub>3</sub> = 25 °C                                                                                                      |                                                                                                  | 1.32  | 2.2   | 2.7   | μS    |

| Soft-Start Time                                                 | T <sub>SOFT</sub>           | T <sub>3</sub> = 25 °C                                                                                                      |                                                                                                  |       | 6.26  |       | ms    |

| CONTROL Current<br>No Switching                                 | I <sub>C(NOSWITCHING)</sub> | T <sub>J</sub> = 25 °C                                                                                                      |                                                                                                  |       | 300   | 450   | μА    |

| C Pin Voltage                                                   | V <sub>C</sub>              | $T_{_{\rm J}} = 25  {}^{\circ}\text{C},  I_{_{\rm C}} = 300  {}^{\circ}$                                                    | μΑ                                                                                               |       | 2.04  | 2.2   | V     |

| Control Current<br>Auto-Restart and End<br>Soft-Start Threshold | I <sub>C(TH)</sub>          | T <sub>1</sub> = 25 °C                                                                                                      |                                                                                                  | 5     | 14    | 25    | μА    |

|                                                                 | I <sub>S1</sub>             | $V_{BP} = V_{BP} + 0.1 \text{ V}$ (Switch not Switching)<br>Exclude $I_{C \text{(NOSWITCHING)}}$<br>$T_{J} = 25 \text{ °C}$ |                                                                                                  |       | 258   | 310   | μА    |

|                                                                 |                             | $V_{BP} = V_{BP} + 0.1 V$                                                                                                   | TNY5071                                                                                          |       | 0.5   | 0.61  | mA    |

| BP Supply Current                                               |                             |                                                                                                                             | TNY5072                                                                                          |       | 0.55  | 0.67  |       |

| ouppiy current                                                  |                             |                                                                                                                             | TNY5073                                                                                          |       | 0.64  | 0.78  |       |

|                                                                 | $I_{S2}$                    | (Switch Switching at 150 kHz)                                                                                               | TNY5074                                                                                          |       | 0.73  | 0.88  |       |

|                                                                 |                             | T <sub>3</sub> = 25 °C                                                                                                      | TNY5075                                                                                          |       | 0.96  | 1.16  |       |

|                                                                 |                             |                                                                                                                             | TNY5076                                                                                          |       | 1.07  | 1.29  |       |

|                                                                 |                             |                                                                                                                             | TNY5077                                                                                          |       | 1.37  | 1.65  |       |

| BP Pin Charge Current                                           | I <sub>CH1</sub>            | $V_{BP} = 0 \text{ V, } T_{J} = 25$                                                                                         | °C                                                                                               | -1.74 | -1.44 | -1.19 | mA    |

|                                                                 | I <sub>CH2</sub>            | $V_{BP} = 4 \text{ V, } T_{J} = 25$                                                                                         | °C                                                                                               | -7.3  | -4.60 | -2.27 |       |

| BP Pin Voltage                                                  | V <sub>BP</sub>             | T <sub>J</sub> = 25 °C                                                                                                      |                                                                                                  | 4.75  | 4.95  | 5.15  | V     |

| BP Pin Voltage<br>Hysteresis                                    | V <sub>BP(H)</sub>          | T <sub>1</sub> = 25 °C                                                                                                      | T <sub>3</sub> = 25 °C                                                                           |       | 0.5   |       | V     |

| BP Shunt Voltage                                                | V <sub>SHUNT</sub>          | $I_{BP} = 2 \text{ mA}$<br>$T_{J} = 25 \text{ °C}$                                                                          |                                                                                                  | 5.15  | 5.40  | 5.65  | V     |

| BP Power-Up Reset<br>Threshold Voltage                          | V <sub>BP(RESET)</sub>      | T <sub>J</sub> = 25 °C                                                                                                      |                                                                                                  | 2.8   | 3.30  | 3.8   | V     |

| V Pin Brown-In<br>Threshold                                     | I <sub>UV+</sub>            | T <sub>3</sub> = 25 °C                                                                                                      |                                                                                                  | 10.9  | 12.2  | 13.3  | μА    |

| Parameter                                          | Symbol             | Conditions  SOURCE = 0 V $T_{J} = -40$ °C to 125 °C  (Unless Otherwise Specified)        | Min  | Тур  | Max  | Units |

|----------------------------------------------------|--------------------|------------------------------------------------------------------------------------------|------|------|------|-------|

| <b>Control Functions (cont.)</b>                   |                    |                                                                                          |      |      |      |       |

| V Pin Brown-Out<br>Threshold                       | I <sub>UV-</sub>   | T <sub>J</sub> = 25 °C                                                                   | 9.2  | 10.3 | 11.4 | μА    |

| <b>Brown-Out Delay Time</b>                        | t <sub>uv-</sub>   | T <sub>1</sub> = 25 °C                                                                   |      | 36   |      | ms    |

| V Pin Line Overvoltage<br>Threshold                | I <sub>OV+</sub>   | T <sub>J</sub> = 25 °C                                                                   | 53.2 | 55.8 | 58.6 | μА    |

| V Pin Line Overvoltage<br>Hysteresis               | I <sub>OV(H)</sub> | T <sub>3</sub> = 25 °C                                                                   |      | 3.9  |      | μА    |

| V Pin Line Overvoltage<br>Recovery Threshold       | I <sub>ov-</sub>   | T <sub>3</sub> = 25 °C                                                                   | 49   |      |      | μА    |

| Line Fault Protection                              |                    |                                                                                          |      |      |      |       |

| VOLTAGE Pin Line<br>Overvoltage Deglitch<br>Filter | t <sub>ov+</sub>   | T <sub>J</sub> = 25 °C<br>See Note B                                                     |      | 3    |      | μS    |

| V Pin Voltage                                      | V <sub>v</sub>     | $T_{_{\mathrm{J}}} = 25  ^{\circ}\mathrm{C}$<br>$I_{_{\mathrm{V}}} = 45  \mathrm{\mu A}$ | 2.2  | 2.6  | 3.0  | V     |

| Parameter                                                      | Symbol                              | Conditions  SOURCE = 0 V $T_{J} = -40  ^{\circ}\text{C} \text{ to } 125  ^{\circ}\text{C}$ (Unless Otherwise Specified) |          | Min  | Тур  | Max  | Units |

|----------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------|------|------|------|-------|

| <b>Circuit Protection</b>                                      |                                     |                                                                                                                         |          |      |      |      |       |

| Standard Current Limit<br>(BP) Capacitor 0.47 μF<br>See Note C |                                     | di/dt = 76 mA/μs                                                                                                        | TNY5071K | 348  | 375  | 402  |       |

|                                                                |                                     | T <sub>1</sub> = 25 °C                                                                                                  | TNY5071V | 348  | 375  | 402  |       |

|                                                                |                                     | $di/dt = 120 \text{ mA/}\mu\text{s}$                                                                                    | TNY5072K | 544  | 585  | 626  |       |

|                                                                |                                     | T <sub>1</sub> = 25 °C                                                                                                  | TNY5072V | 544  | 585  | 626  |       |

|                                                                |                                     | di/dt = 176 mA/μs                                                                                                       | TNY5073K | 757  | 815  | 873  |       |

|                                                                | I <sub>LIMIT</sub>                  | $T_{\rm j} = 25  ^{\circ}\text{C}$                                                                                      | TNY5073V | 757  | 815  | 873  | mA    |

|                                                                | (Switch<br>Switching at<br>150 KHz) | di/dt = 205 mA/ $\mu$ s<br>T <sub>1</sub> = 25 °C                                                                       | TNY5074K | 892  | 960  | 1028 |       |

|                                                                |                                     |                                                                                                                         | TNY5074V | 892  | 960  | 1028 |       |

|                                                                |                                     | $di/dt = 259 \text{ mA/}\mu\text{s}$<br>$T_{_{J}} = 25 \text{ °C}$                                                      | TNY5075K | 1125 | 1210 | 1295 |       |

|                                                                |                                     |                                                                                                                         | TNY5075V | 1125 | 1210 | 1295 |       |

|                                                                |                                     | di/dt = 410 mA/ $\mu$ s<br>T $_{_{\mathrm{J}}}$ = 25 °C                                                                 | TNY5075E | 1794 | 1930 | 2066 |       |

|                                                                |                                     | di/dt = 619 mA/ $\mu$ s<br>T $_{_{\mathrm{J}}}$ = 25 °C                                                                 | TNY5076E | 2323 | 2500 | 2677 |       |

|                                                                |                                     | di/dt = 690 mA/ $\mu$ s<br>T $_{_{J}}$ = 25 °C                                                                          | TNY5077E | 3013 | 3240 | 3467 |       |

| BYPASS Pin Fault Shut-<br>Down Threshold Current               | $I_{SD}$                            | T <sub>1</sub> = 25 °C                                                                                                  |          | 3.5  | 7    | 11   | mA    |

| Auto-Restart On-Time                                           | t <sub>AR</sub>                     | T <sub>3</sub> = 25 °C                                                                                                  |          |      | 63   |      | ms    |

| Auto-Restart Off-Time                                          | t <sub>AR(OFF)</sub>                | T <sub>3</sub> = 25 °C                                                                                                  |          |      | 1.2  |      | sec   |

| Short Auto-Restart<br>Off-Time                                 | t <sub>AR(OFF)SH</sub>              | T <sub>J</sub> = 25 °C<br>See Note B                                                                                    |          |      | 0.2  |      | sec   |

| Parameter                      | Symbol              | SOURC<br>T <sub>1</sub> = -40 °                                                    | litions<br>CE = 0 V<br>C to 125 °C<br>wise Specified)                                               | Min | Тур   | Max   | Units |

|--------------------------------|---------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|-------|-------|-------|

| Output                         |                     |                                                                                    |                                                                                                     |     |       |       |       |

|                                |                     | TNY5071K/V                                                                         | T <sub>1</sub> = 25 °C                                                                              |     | 9.14  | 10.53 |       |

|                                |                     | $I_D = 225 \text{ mA}$                                                             | T <sub>1</sub> = 100 °C                                                                             |     | 13.75 | 15.84 |       |

|                                |                     | TNY5072K/V                                                                         | T <sub>1</sub> = 25 °C                                                                              |     | 5.94  | 6.85  |       |

|                                |                     | $I_D = 351 \text{ mA}$                                                             | T <sub>3</sub> = 100 °C                                                                             |     | 8.75  | 10.10 |       |

|                                |                     | TNY5073K/V                                                                         | T <sub>1</sub> = 25 °C                                                                              |     | 4.23  | 4.88  |       |

|                                |                     | $I_D = 489 \text{ mA}$                                                             | T <sub>3</sub> = 100 °C                                                                             |     | 7.12  | 8.21  |       |

|                                |                     | TNY5074K/V                                                                         | T <sub>J</sub> = 25 °C                                                                              |     | 2.93  | 3.38  | Ω     |

| ON-State Resistance            | R <sub>DS(ON)</sub> | $I_D = 576 \text{ mA}$                                                             | T <sub>1</sub> = 100 °C                                                                             |     | 4.35  | 5.02  |       |

|                                |                     | TNY5075K/V<br>I <sub>D</sub> = 726 mA                                              | T <sub>J</sub> = 25 °C                                                                              |     | 1.80  | 2.08  |       |

|                                |                     |                                                                                    | T <sub>J</sub> = 100 °C                                                                             |     | 2.60  | 3.01  |       |

|                                |                     | $ TNY5075E $ $ I_{D} = 1158 \text{ mA} $                                           | T <sub>J</sub> = 25 °C                                                                              |     | 1.91  | 2.21  |       |

|                                |                     |                                                                                    | T <sub>J</sub> = 100 °C                                                                             |     | 2.90  | 3.35  |       |

|                                |                     | TNY5076E<br>I <sub>D</sub> = 1500 mA                                               | T <sub>J</sub> = 25 °C                                                                              |     | 1.70  | 1.97  |       |

|                                |                     |                                                                                    | T <sub>J</sub> = 100 °C                                                                             |     | 2.60  | 3.00  |       |

|                                |                     | TNY5077E                                                                           | T <sub>J</sub> = 25 °C                                                                              |     | 1.16  | 1.34  |       |

|                                |                     | $I_D = 1944 \text{ mA}$                                                            | T <sub>1</sub> = 100 °C                                                                             |     | 1.75  | 2.02  |       |

| OFF-State Drain                | I <sub>DSS1</sub>   |                                                                                    | $V_{BP} = V_{BP} + 0.1 \text{ V}$ $V_{DS} = 80\% \text{ Peak Drain Voltage}$ $T_1 = 125 \text{ °C}$ |     |       | 200   | μА    |

| Leakage Current                | $I_{	extsf{DSS2}}$  | $V_{BP} = V_{BP} + 0.1 \text{ V}$ $V_{DS} = 325 \text{ V}$ $T_{1} = 25 \text{ °C}$ |                                                                                                     |     | 15    |       | μА    |

| Drain Supply Voltage           |                     | See Note B                                                                         |                                                                                                     | 30  |       |       | V     |